학습 개요

- 디지털 회로를 바탕으로 명령어를 처리하기 위한 처리 장치와 제어 장치가 어떻게 구현되고 동작하는 지를 살펴봄

- 입 출력 시스템의 구조와 제어 방식, 그리고 병렬 처리의 기법에 대해서 학습함

학습 목표

- 명령어의 종류, 형식, 그리고 주소 지정 방식 이해할 수 있음

- 중앙 처리 장치의 구성, 동작 원리 및 구현 방법을 이해할 수 있음

- 입 출력 시스템의 구성과 제어 방식, 그리고 병렬 처리 기법으로서 파이프라인 처리의 개념과 동작을 이해할 수 있음

강의록

명령어

명령어 집합 구조

- 내장 프로그램 개념으로부터 직접적으로 도출된 개념

- ISA (Instruction Set Architecture)

- HW와 SW의 교량 역할을 하는 개념

- 명령어 집합

- 컴퓨터 시스템 내에 정의되어 있는 기본적인 명령어들의 집합

- 모든 컴퓨터는 자신만의 명령어 집합을 가짐

- 명령어 종류, 명령어 형식, 주소 지정 방식 등을 고려해서 결정됨

- 명령어 집합이 결정되면 그에 상응하는 하드웨어 구조가 결정됨

- ISA (Instruction Set Architecture)

명령어 집합에 따른 컴퓨터 구조

- CISC 복합 명령어 집합 컴퓨터, Complex Instruction Set Computer

- 복합 명령어를 포함하여 명령어와 주소 지정 방식의 수를 많이 사용

- 수많은 복잡한 명령어를 탑재/사용함으로써 프로그램에서 사용되는 전체 명령어의 개수를 줄여서 프로그램의 실행 시간 단축을 위한 구조

- 연산 코드 해독 및 실행을 위한 제어 장치가 복잡해지는 단점을 가짐

- 복합 명령어를 포함하여 명령어와 주소 지정 방식의 수를 많이 사용

- RISC 단축 명령어 집합 컴퓨터, Reduced Instruction Set Computer

- 명령어를 단순화하고 개수를 줄이고 하드웨어를 간단히 개선 시킨 구조

- 각 명령어의 길이를 균일하게 짧게 함으로써 각 명령어의 실행 시간을 최소화

- 많은 처리량과 빠른 속도를 지향

- 제어 장치는 비교적 간단하며, 일반적 하드웨어로 구성

- 각 명령어의 길이를 균일하게 짧게 함으로써 각 명령어의 실행 시간을 최소화

- 명령어를 단순화하고 개수를 줄이고 하드웨어를 간단히 개선 시킨 구조

기본적인 명령어 종류

- 데이터 전송 명령어

- 데이터 이동

- 레지스터 ↔ 레지스터, 주 기억 장치 ↔ 레지스터, 기억 장치 ↔ 기억 장치 등

- 데이터 이동

- 데이터 처리 명령어

- 산술 명령어, 논리 연산 명령어, 비트 단위 명령어, 시프트 명령어 등

- 프로그램 제어 명령어

- 프로그램의 제어 흐름 관리

- 무조건적 분기

- 조건적 분기

- 프로그램의 제어 흐름 관리

- 입출력 명령어

- 보조 기억 장치 및 입 출력 장치 등의 정보 교환 명령어, 인터럽트 관련 명령어

- 인터럽트

- 프로그램의 정상 수행을 멈추고, CPU 이외의 다른 장치의 요구 사항을 수행하는 기능

- 인터럽트

- 보조 기억 장치 및 입 출력 장치 등의 정보 교환 명령어, 인터럽트 관련 명령어

명령어 형식

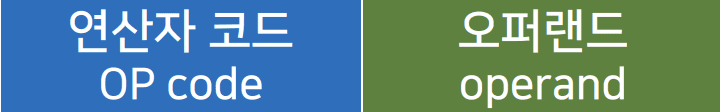

- 기본 형식

- 각 명령어는 실행에 필요한 모든 정보를 포함해야 함

- 연산자 코드

- CPU가 처리할 연산의 종류

- 할당된 비트 수

- CPU가 수행할 수 있는 최대 명령어 개수

- 오퍼랜드(피 연산자)

- 명령어가 사용할 데이터 또는 데이터가 저장되어 참조될 기억 장치의 주소

- 오퍼랜드의 크기/개수

- 명령어 집합, 명령어 등 컴퓨터 구조에 따라 달라짐

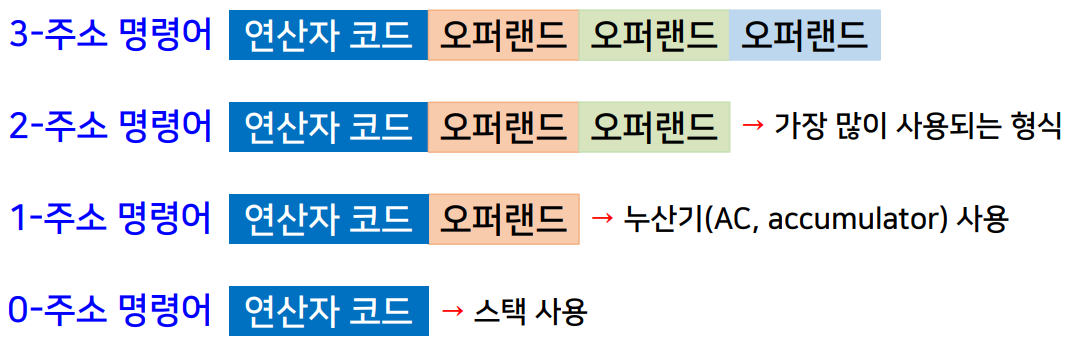

- 오퍼랜드 개수에 따른 구분

-

연산의 대상이 되는 데이터가 어디서 추출되고, 결과가 어디에 저장할 지에 따른 구분

-

-

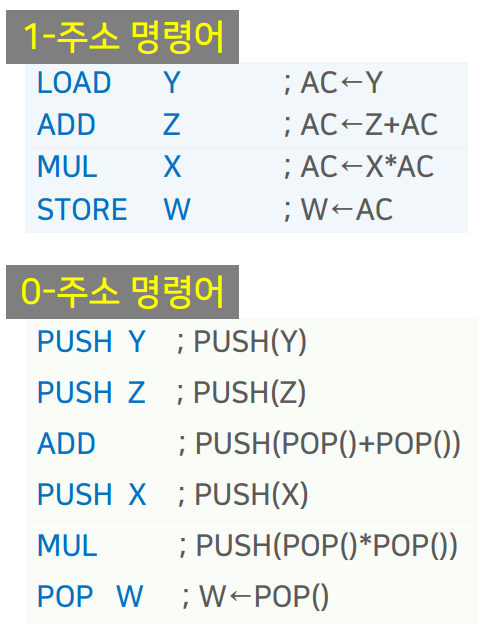

W = X ∗ (Y + Z)

-

명령어의 메모리 표현

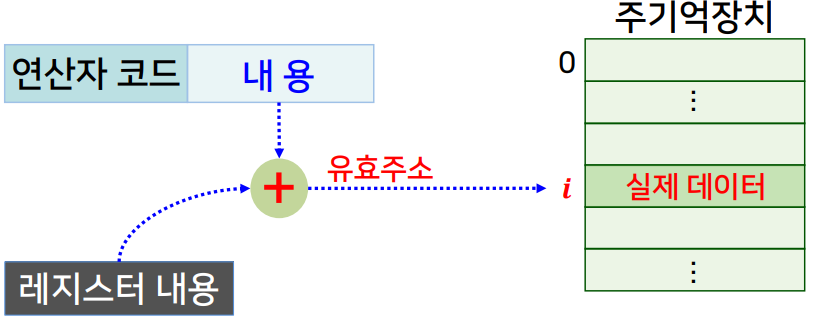

주소 지정 방식 addressing mode

- 연산에 사용될 데이터가 기억 장치의 어디에 위치하는 지를 지정하는 방법

- 명령어 개수/길이를 줄이고, 기억 장치 사용에 대한 융통성 증가 시킴

- 유효 주소 effective address

- 주소 지정 방식에 의해 계산되어 실제 데이터가 저장된 주소

- 빠른 접근 순

- 즉시 주소 지정 방식

- 레지스터 주소 지정 방식

- 직접 주소 지정 방식

- 상대 주소 지정 방식

- 간접 주소 지정 방식

-

즉시 immediate 주소 지정 방식

-

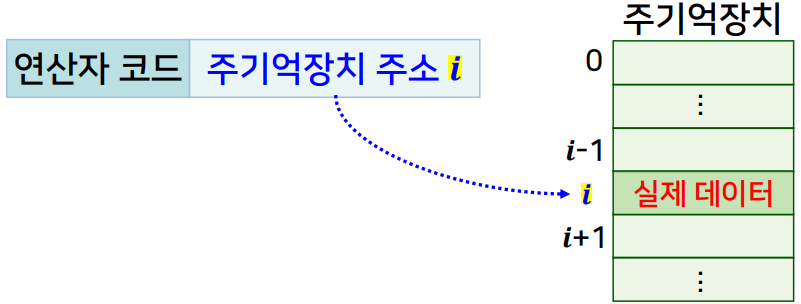

직접 direct 주소 지정 방식

-

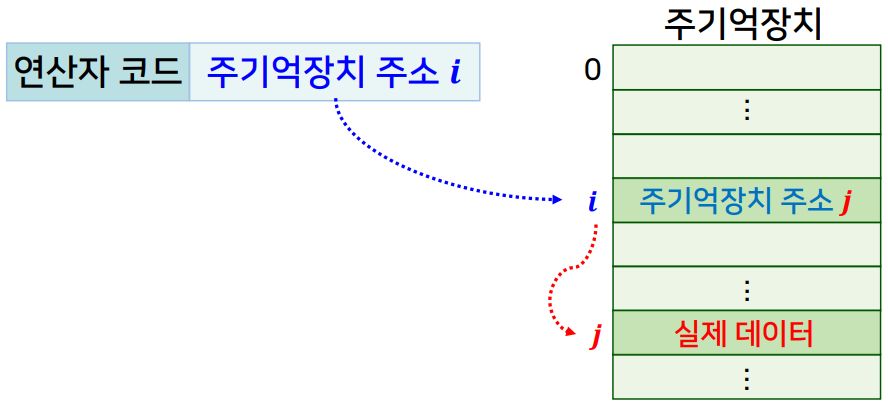

간접 indirect 주소 지정 방식

-

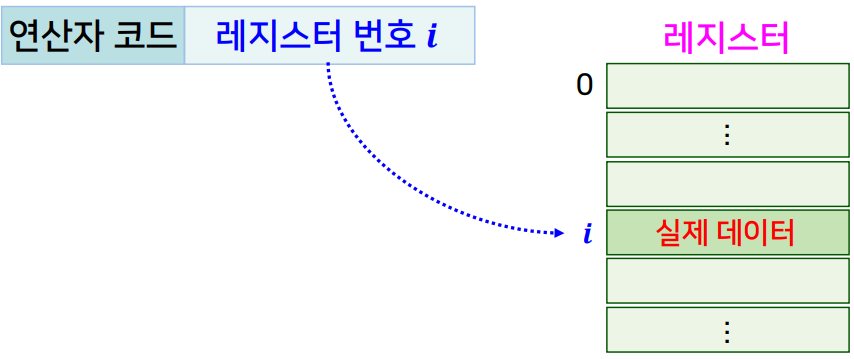

레지스터 register 주소 지정 방식

-

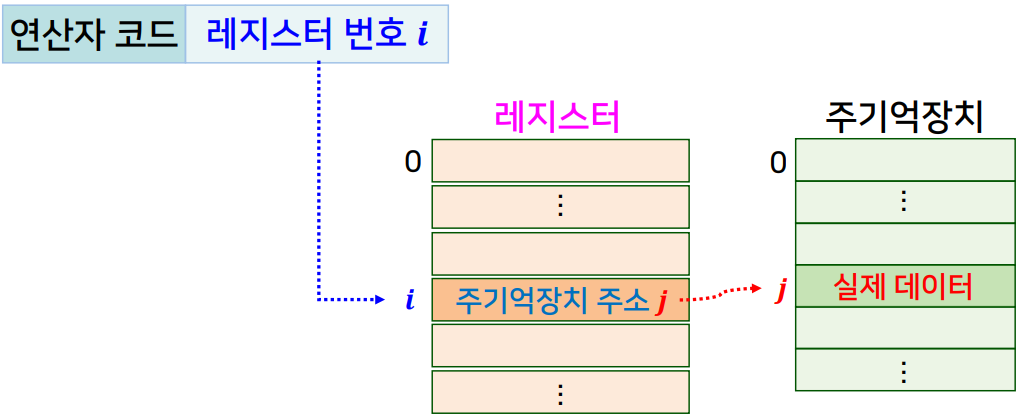

레지스터 간접 register-indirect 주소 지정 방식

-

상대 relative 주소 지정 방식

- 프로그램 카운터

- 분기형 명령어에서 주로 사용

- 인덱스 레지스터

- 인덱스 된 주소 지정 방식

- 배열 인덱싱에 주로 사용

- 인덱스 된 주소 지정 방식

- 베이스 레지스터

- 베이스 레지스터 주소 지정 방식

- 프로그램 카운터

중앙 처리 장치

명령어를 하드웨어에 구현하는 방법

- 마이크로 프로그램에 의한 제어 장치

- Micro-programed control device

- 산술/논리 연산과 명령어 수행 순서 조작 회로가 제어 기억 장치에 저장 된 비트 패턴(마이크로 연산)으로 가동하는 장치

- 각 명령어는 여러 개의 마이크로 연산으로 구현

- 명령어 집합의 변경이나 명령어 추가 등이 용이

- CISC 컴퓨터 구조에서 주로 사용

- 직접 회로로 구성된 제어 장치

- Hard-wired control device

- 연산과 명령어 수행 회로가 기억 장치에 의존하지 않고 직접 구성된 제어 회로에 의해 기동하는 장치

- 빠른 수행, 명령어 집합의 변경에 쉽게 적응할 수 없음

- 명령어 수가 적은 RISC 컴퓨터 구조에서 주로 사용

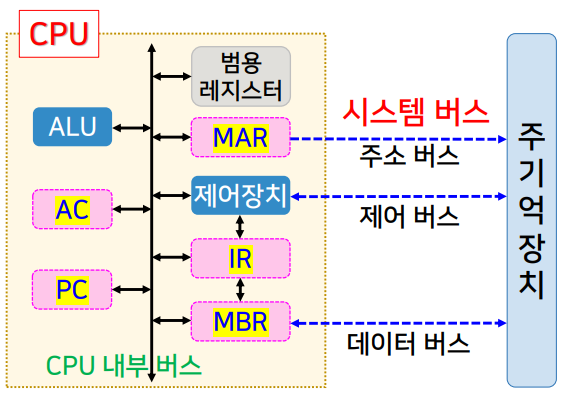

레지스터

-

범용 레지스터, 특수 레지스터

- 누산기 AC, Accumulator

- 데이터나 연산 결과를 일시적으로 저장하는 레지스터

- 기억 장치 버퍼 레지스터 MBR, Memory Buffer Register

- 기억 장치에 저장 될 또는 기억 장치에서 읽어온 데이터를 임시로 저장

- 기억 장치 주소 레지스터 MAR, Memory Address Register

- 현재의 PC 내용을 시스템 버스의 주소 버스로 출력하기 전에 일시적으로 저장

- PC 내용

- 다음에 수행될 명령어가 저장되어 있는 기억 장소의 주소

- PC 내용

- 현재의 PC 내용을 시스템 버스의 주소 버스로 출력하기 전에 일시적으로 저장

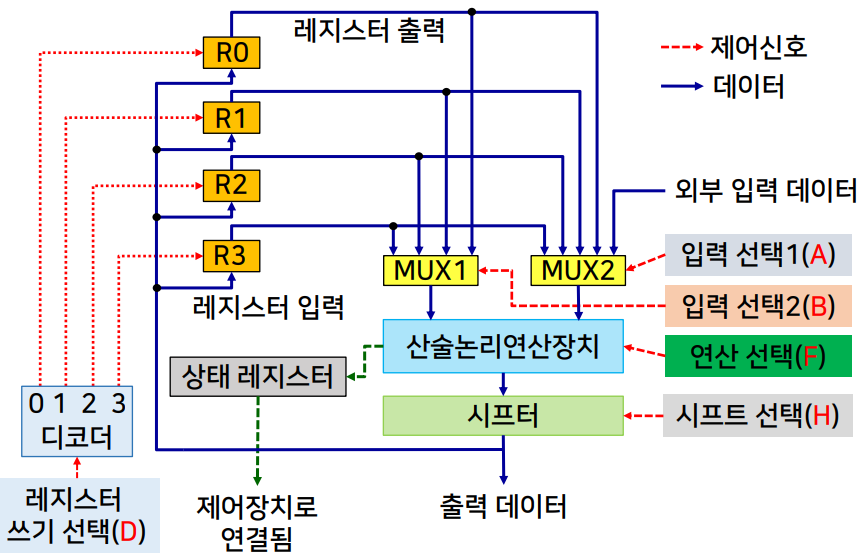

처리 장치

- 연산 장치 + 레지스터를 묶어서 일컫는 표현으로 사용

- 모든 기능은 비트 패턴으로 구성 된 마이크로 연산으로 구현

- 마이크로 연산의 분류

- 레지스터 전송 마이크로 연산

- R0 ← R1

- 산술 마이크로 연산

- R0 ← R1 + R2

- R2 ← R1 - R2

- R1 ← R1 - 1

- 논리 마이크로 연산

- R1 ← R2’

- R0 ← R1 ∧ R2

- R0 ← R1 ∨ R2

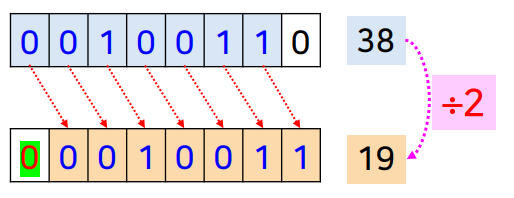

- 시프트 마이크로 연산

- R1 ← shl R2

- R1 ← shr R2

- 레지스터 전송 마이크로 연산

시프트 연산

-

왼쪽 시프트

-

오른쪽 시프트

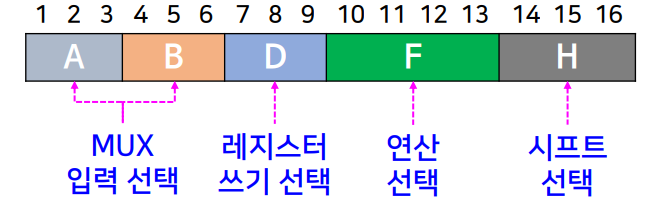

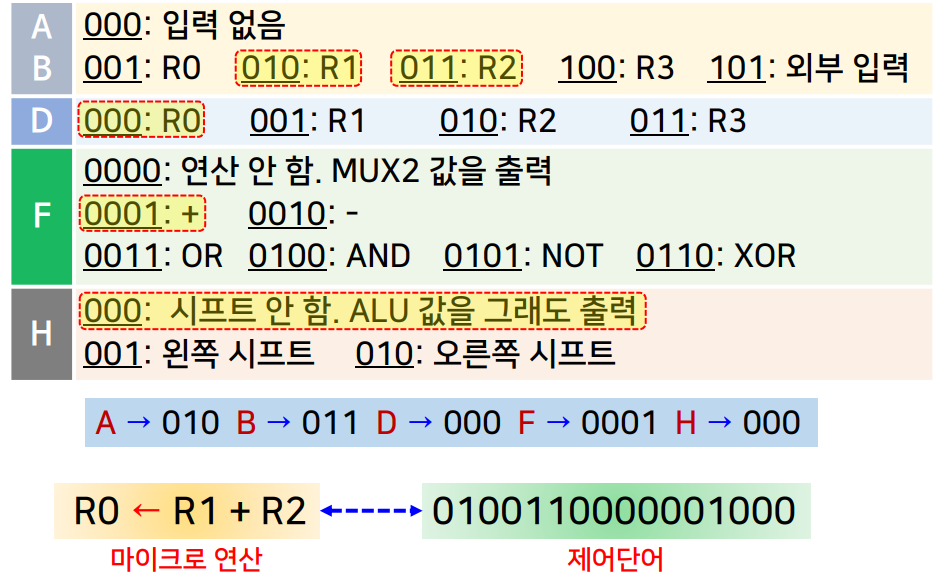

제어 단어

- 마이크로 연산을 처리 장치에 직접 다루기 위해서 필요

- 각 비트들이 처리 장치의 논리 회로 내의 각종 MUX와 디코더의 선택 제어 선으로 연결되어 하드웨어를 회로 수준에서 직접적으로 통제하기 위한 것

- 각 마이크로 연산은 제어 단어와 일대일 매핑

-

ex) 16비트 제어 단어

처리 장치의 구성

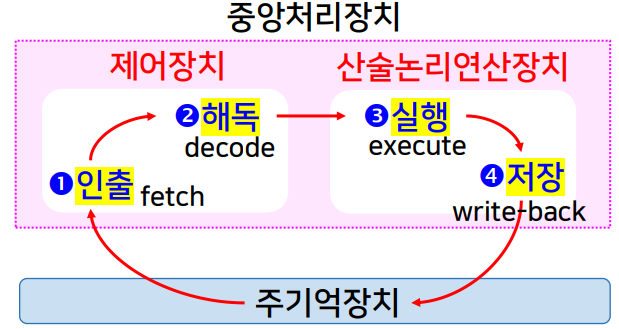

제어 장치

- 메모리에 저장 된 명령을 어떻게 순차적으로 가져와서 수행할 것인 가를 통제하는 것

- 두 가지의 기본적인 기능

- 처리 장치를 구동해서 특정 연산을 수행한 후 처리 장치 내의 레지스터 값을 갱신하고 연산 결과를 출력

- 현재 주어진 명령을 수행한 후 다음에 수행할 명령의 주소 정보를 생성

- 두 가지의 기본적인 기능

-

명령어 사이클(instruction cycle)

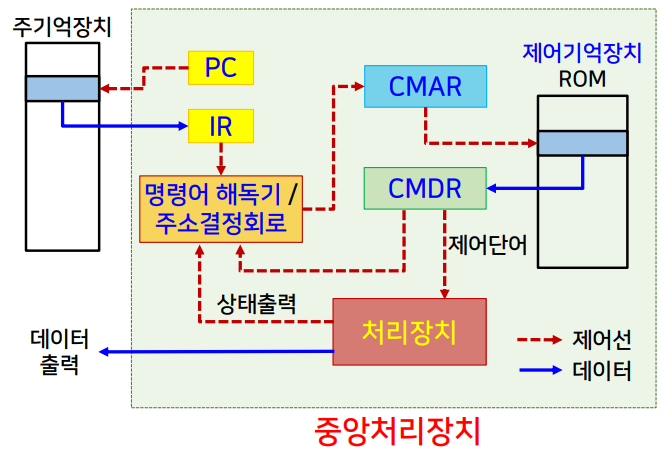

제어 장치의 구성 요소

- 프로그램 카운터 PC, Program Counter

- 다음에 수행될 명령어가 저장되어 있는 주 기억 장치에 주소 저장

- 명령어 레지스터 IR, Instruction Register

- 주 기억 장치에서 인출되어 현재 실행 중인 명령어 저장

- 제어 기억 장치 control memory

- 마이크로 연산의 집합을 저장하고 있는 기억 장치

- ROM으로 구현

- 마이크로 연산의 집합을 저장하고 있는 기억 장치

- 명령어 해독기

- 주어진 명령어를 제어 기억 장치의 해당 마이크로 명령이 시작하는 주소로 매핑해 주는 것

- 주소 결정 회로

- 명령어에 포함된 주소 정보, 제어 단어와 연결된 주소 정보, 처리 장치 구동 후 결과로 나오는 상태 비트 등으로부터 제어 기억 장치의 다음 수행할 마이크로 명령의 주소를 생성

- 제어 기억 장치 주소 레지스터 CMAR

- 제어 기억 장치에서 다음에 수행할 마이크로 명령의 위치를 가리키는 주소 저장

- 제어 기억 장치 데이터 레지스터 CMDR

- 제어 기억 장치에서 가져온 다음 수행할 마이크로 연산 저장

- CMDR 없이 제어 기억 장치의 출력이 직접 다른 장치들로 연결 가능

제어 장치의 구성

입 출력 장치 및 병렬 처리

입 출력 시스템

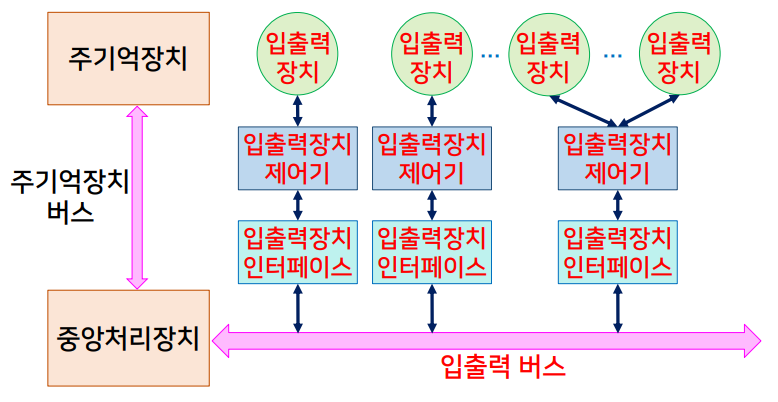

-

기본 입 출력 시스템의 구성도

입 출력 시스템의 기본 구성 요소

- 입 출력 장치

- 사용자와 컴퓨터 시스템을 연결해 주는 장치

- 키보드, 마우스, 모니터, 프린터, 디스크 등

- 사용자와 컴퓨터 시스템을 연결해 주는 장치

- 입 출력 장치 제어기

- 상이한 기계적/전자적 특성을 가진 입 출력 장치를 물리적/전자적으로 제어해서 구동 시키는 작업을 수행하는 기기

- 모터 회전, 헤드 이동, 입출력 매체의 위치 정렬 등의 작업 수행

- 제어기가 입 출력 장치에 포함된 경우 및 하나의 제어기로 여러 입 출력 장치를 제어하는 경우도 존재

- 상이한 기계적/전자적 특성을 가진 입 출력 장치를 물리적/전자적으로 제어해서 구동 시키는 작업을 수행하는 기기

- 입 출력 장치 인터페이스

- 입 출력 장치와 중앙 처리 장치/주 기억 장치 사이의 데이터 전송 속도, 데이터 처리 단위, 오류 확률의 차이를 상쇄해서 올바른 전송을 위한 방법 제공

- 입 출력 버스

- 입 출력 전용으로 사용되는 정보 회선의 묶음

- 입 출력 장치와 중앙 처리 장치 사이의 정보 교환에 사용

- 여러 장치에 의한 버스 사용 충돌을 막기 위한 중재기가 필요

- 입 출력 전용으로 사용되는 정보 회선의 묶음

입출력 제어 방식

- CPU에 의한 제어

- 독립된 입출력 제어기가 없이 입 출력 장치의 정보가 CPU를 통해 주 기억 장치에 쓰고 읽혀지는 방식

- CPU의 관여 시점

- 프로그램에 의한 방식

- CPU가 주기적으로 입 출력 장치에 신호를 보내 입출력 여부를 물어보는 방식

- 인터럽트에 의한 방식

- 입 출력 장치가 인터럽트를 통해 입출력 요청이 있을 때만 CPU가 하던 일을 중단하고 해당 장치와 연락하는 방식

- 프로그램에 의한 방식

- DMA 방식 (Direct Memory Access)

- 입 출력 장치가 주 기억 장치와 직접 연결

- CPU는 두 장치 간의 초기 설정 및 허가에만 관여

- 직접적인 정보의 이동은 장치 간에 DMA 제어기가 해결

- 채널 방식

- 채널(입출력 전용의 별도 프로세서) 사용

- 정보 전송 통로 제공 및 CPU와 같은 산술/논리/분기 연산 작업도 수행 가능

- 채널(입출력 전용의 별도 프로세서) 사용

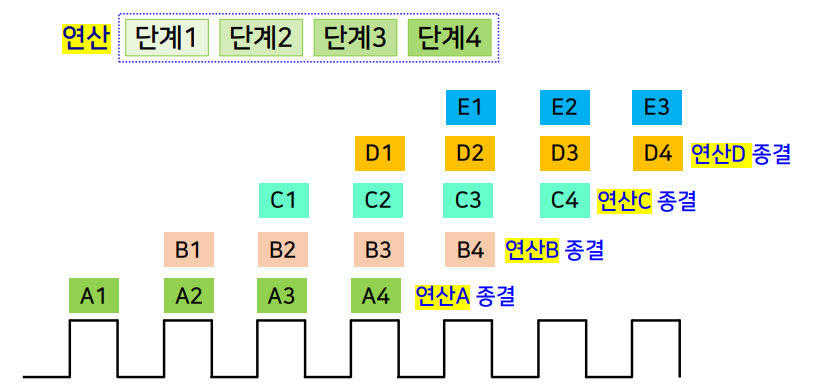

병렬 처리

- 파이프라인 처리기 pipeline processor

- 프로그램 내에 내재하고 있는 시간적 병렬성을 활용하는 방법

- CPU 내의 하드웨어 요소의 일부를 파이프라인 형태로 구성하여 프로그램 수행에 필요한 작업을 시간적으로 중첩하여 수행 시키는 처리기

- 하나의 연산을 서로 다른 기능을 가진 여러 개의 단계(세그먼트)로 분할하여, 각 단계가 동시에 서로 다른 데이터를 취급하도록 함

- 현재 명령의 특정 단계가 끝나고 다음 단계로 넘어가면 바로 다른 명령을 불러들여서 해당 단계를 동시에 처리하는 방식

- 연달아 수행될 명령어들은 서로 간의 간섭이 없어야 함

- 멀티 코어 구조

- 하나의 CPU에 2개 이상의 코어를 넣어서 동시에 여러 개의 명령어를 처리할 수 있는 구조

- 코어

- CPU의 일부분으로 명령을 가져와 수행하는 회로

- 각 코어는 수행 중인 응용 프로그램의 프로세스나 스레드를 하나씩 담당

- 코어

- 하나의 CPU에 2개 이상의 코어를 넣어서 동시에 여러 개의 명령어를 처리할 수 있는 구조

- GPGPU General Purpose computing on Graphics Processing Unit

- 그래픽스 처리 장치를 사용한 범용 연산

- 그래픽 카드의 고도의 병렬 처리 능력을 연산에 사용하는 기술

정리 하기

- 명령어

- 명령어 집합 구조

- 내장 프로그램 개념으로부터 직접적으로 도출된 개념

- 컴퓨터 시스템 내에 정의된 기본적인 명령어들의 집합

- CISC ↔ RISC

- 복합 명령어 집합 컴퓨터(CISC)와 단축 명령어 집합 컴퓨터(RISC)의 특징 비교

- 명령어 종류와 형식

- 데이터 전송 명령어

- 데이터 처리 명령어

- 프로그램 제어 명령어

- 입출력 명령어

- 기본 형식

- (연산자 코드, 오퍼랜드)

- 오퍼랜드 개수에 따른 구분 (3-주소, 2-주소, 1-주소, 0-주소)

- 주소 지정 방식

- 연산에 사용될 데이터가 기억 장치의 어디에 위치하는 지를 지정하는 방법

- 즉시, 레지스터, 직접, 상대, 간접 주소 지정 방식

- 연산에 사용될 데이터가 기억 장치의 어디에 위치하는 지를 지정하는 방법

- 명령어 집합 구조

- 중앙 처리 장치

- 명령어 구현 방법

- 마이크로 프로그램

- 제어 기억 장치에 저장된 비트 패턴(마이크로 연산)으로 가동

- CISC에서 주로 사용

- 직접 회로

- 연산과 명령어 수행 회로가 기억 장치에 의존하지 않고 직접 구성된 제어 회로에 의해 기동

- RISC에서 주로 사용

- 마이크로 프로그램

- 특수 레지스터

- AC (Accumulator)

- 데이터나 연산 결과를 일시적으로 저장하는 레지스터

- PC (Program Counter)

- 다음에 수행될 명령어가 저장되어 있는 주 기억 장치의 주소 저장

- IR (Instruction Register)

- 주 기억 장치에서 인출되어 현재 실행 중인 명령어 저장

- MAR (Memory Address Register)

- 현재의 PC 내용을 시스템 버스의 주소 버스로 출력하기 전에 일시적으로 저장

- MBR (Memory Buffer Register)

- 기억 장치에 저장될 또는 기억 장치에서 읽어온 데이터를 임시로 저장

- AC (Accumulator)

- 제어 단어와 처리 장치 구성

- 마이크로 연산을 처리 장치에 직접 다루기 위해 필요

- 각 마이크로 연산은 제어 단어와 일대일 매핑

- 제어 장치

- 기능

- 메모리에 저장 된 명령을 순차적으로 가져와 수행하는 것 통제

- 처리 장치 구동 및 레지스터 값 갱신

- 다음 수행할 명령의 주소 정보 생성

- 명령어 사이클(인출-해독-실행-저장)

- 명령어가 CPU에 의해 처리되는 과정

- 구성 요소

- 프로그램 카운터(PC)

- 명령어 레지스터(IR)

- 제어 기억 장치(control memory)

- 명령어 해독기

- 주소 결정 회로

- 제어 기억 장치 주소 레지스터(CMAR)

- 제어 기억 장치 데이터 레지스터(CMDR)

- 동작

- 기능

- 명령어 구현 방법

- 입 출력 장치 및 병렬 처리

- 입 출력 시스템의 구성 요소

- 입 출력 장치

- 사용자와 컴퓨터 시스템을 연결해 주는 장치

- 입 출력 장치 제어기

- 상이한 특성을 가진 입 출력 장치를 물리적/전자적으로 제어

- 입 출력 장치 인터페이스

- 입 출력 장치와 중앙 처리 장치/주 기억 장치 사이의 데이터 전송 속도, 처리 단위, 오류 확률 차이 상쇄

- 입 출력 버스

- 입 출력 전용으로 사용되는 정보 회선의 묶음

- 입 출력 장치

- 입출력 제어 방식

- CPU(프로그램, 인터럽트)

- CPU가 직접 제어

- 프로그램에 의한 방식

- 인터럽트에 의한 방식

- CPU가 직접 제어

- DMA (Direct Memory Access)

- 입 출력 장치가 주 기억 장치와 직접 연결

- CPU는 초기 설정 및 허가만 관여

- 채널

- 입출력 전용 프로세서(채널)를 사용하여 데이터 전송 및 산술/논리/분기 연산 수행

- CPU(프로그램, 인터럽트)

- 병렬 처리

- 파이프라인 처리

- 프로그램 내 시간적 병렬성을 활용

- CPU 하드웨어 요소를 파이프라인 형태로 구성하여 작업 시간 중첩 수행

- 멀티 코어 구조

- 하나의 CPU에 2개 이상의 코어를 넣어 동시에 여러 명령어 처리

- GPGPU

- 그래픽스 처리 장치를 사용한 범용 연산, 그래픽 카드의 고도 병렬 처리 능력 활용

- 파이프라인 처리

- 입 출력 시스템의 구성 요소

연습 문제

-

연산의 대상이 되는 데이터를 누산기에서 가져오고, 결과를 누산기에 저장하는 방식의 명령어 형식은?

a. 1-주소 명령어

- 연산의 대상이 되는 데이터를 어디서 추출하고 결과를 어디에 저장할 지에 따라, 즉 오퍼랜드의 개수에 따라 명령어 형식은 0/1/2/3-주소 명령어로 구분할 수 있음

- 0-주소 명령어

- 스택 구조의 컴퓨터에서 사용

- 1-주소 명령어

- 누산기(AC)를 이용하는 형식

- 2-주소 명령어

- 가장 보편적으로 사용되는 형식

- 3-주소 명령어

- 프로그램의 길이가 가장 짧음

-

주소 지정 방식 중에서 두 번의 기억 장치 접근이 필요한 것은?

a. 간접 주소 지정 방식

- 간접 주소 지정 방식은 명령어의 오퍼랜드의 내용이 실제 데이터가 저장된 기억 장치의 주소를 가지고 있는 기억 장치의 주소를 나타내기 때문에 두 번의 기억 장치 접근을 통해서 실제 데이터를 얻기 때문에 처리 속도가 가장 느림

- 주소 지정 방식에 따른 접근 속도의 비교(감소 순 나열)

- 즉시 주소 지정 방식 → 레지스터 주소 지정 방식 → 직접 주소 지정 방식 → 상대 주소 지정 방식 → 간접 주소 지정 방식

-

주 기억 장치에서 가져와서 현재 실행 중인 명령어를 저장하고 있는 레지스터는?

a. IR

- CPU 내에서 특별한 기능을 수행하는 특수 레지스터로서는 다음과 같은 것들이 있음

- 누산기(AC)

- 데이터나 연산 결과를 일시적으로 저장하는 레지스터로서, 입력 장치로부터 데이터를 받아들이거나 출력 장치로 데이터를 전송하는 데 사용함

- CPU가 연산을 수행한 후 그 결과는 반드시 누산기에 저장 됨

- 프로그램 카운터(PC)

- 다음에 수행 될 명령어가 저장 되어 있는 주 기억 장치의 주소를 저장하고 있는 레지스터

- 명령어 레지스터(IR)

- 주 기억 장치에서 가져와서 현재 실행 중인 명령어를 저장하고 있는 레지스터

- 기억 장치 버퍼 레지스터(MBR)

- 기억 장치에 저장 될 또는 기억 장치에 읽어온 데이터를 임시로 저장하는 레지스터

- 기억 장치 주소 레지스터(MAR)

- 현재 프로그램 카운터(PC)의 내용을 시스템 버스의 주소 버스로 출력 되기 전에 일시적으로 저장 되는 레지스터

- 누산기(AC)

- CPU 내에서 특별한 기능을 수행하는 특수 레지스터로서는 다음과 같은 것들이 있음

-

제어 장치의 명령어 사이클을 올바르게 나열한 것은?

a. 인출 – 해독 – 실행 - 저장

- 명령어 사이클

- 인출 – 해독 – 실행 - 저장

- 제어 장치는 처리 장치 및 기억 장치와 연결 되어 있어서 기억 장치로부터 다음에 수행할 명령어를 가져와서(인출, fetch) 상응하는 마이크로 연산들로 해독(decode)한 후 수행(execute)하고 레지스터에 다시 저장하는 과정을 반복 수행함

- 명령어 사이클

-

입 출력 제어 방식 중에서 입 출력 전용의 별도 프로세서를 사용하기 때문에 CPU와 같은 다양한 연산 작업도 수행 가능한 것은?

a. 채널 방식

- 입 출력 제어 방식

- CPU를 통한 제어

- 입 출력 장치의 정보가 CPU를 통해 주 기억 장치에 쓰고 읽혀지는 방식

- 프로그램에 의한 방식

- CPU가 주기적으로 입 출력 장치에 신호를 보내 입출력이 필요한 지를 물어보는 방식

- 인터럽트 방식

- 입 출력 장치가 인터럽트를 걸 때만 CPU가 해당 장치와 연락하는 방식

- DMA 방식

- 작업을 수행하다가 CPU가 입 출력을 원할 때 DMA 제어기에게 입 출력을 지시하고, CPU는 다른 작업을 처리

- 지시를 받은 DMA 제어기는 CPU를 거치지 않고 주 기억 장치와 입 출력 장치 사이의 데이터 전송을 수행

- 전송이 끝나면 DMA 제어기는 CPU에게 인터럽트 신호를 보냄으로써 동작을 마치고, 신호를 받은 CPU는 입출력 요청 이후의 작업을 재개함

- 채널 방식

- 입출력 전용의 별도의 프로세서(채널)를 사용하는 방식으로, 입출력에 대한 CPU의 부담이 거의 없으나 하드웨어적인 비용이 증가하는 단점이 있음

- CPU를 통한 제어

- 입 출력 제어 방식

정리 하기

- 명령어

- 명령어 집합

- 컴퓨터 시스템 내에 정의된 기본적인 명령어들의 집합

- 명령어 집합이 정의되면 그에 상응하는 하드웨어 구조가 결정됨 → CISC, RISC

- 명령어 형식

- 연산자 코드와 오퍼랜드로 구성

- 오퍼랜드의 개수에 따른 구분

- 3-주소 명령어

- 2-주소 명령어

- 1-주소 명령어

- 0-주소 명령어

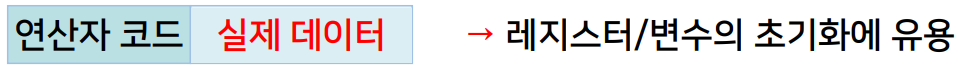

- 명령어의 메모리 표현

- 각 연산자에게 고유의 이진 패턴이 부여되고, 주 기억 장치의 주소와 레지스터도 고유의 이진 패턴이 부여되며, 이런 연산자 코드-오퍼랜드 쌍이 2진수의 나열의 형태로 표현되어 주 기억 장치에 저장됨

- 주소 지정 방식

- 연산에 사용 될 데이터가 기억 장치의 어디에 위치하는 지를 지정하는 방식

- 종류

- 즉시 주소 지정 방식

- 직접 주소 지정 방식

- 간접 주소 지정 방식

- 레지스터 주소 지정 방식

- 레지스터 간접 주소 지정 방식

- 상대 주소 지정 방식

- 인덱스 된 주소 지정 방식

- 베이스 레지스터 주소 지정 방식

- 명령어 집합

- 중앙 처리 장치

- 명령어의 구현 방법

- 마이크로 프로그램에 의한 제어 장치

- 연산과 명령어 수행 순서 조작 회로가 제어 기억 장치에 저장된 마이크로 프로그램으로 기동하는 장치

- 직접 회로로 구성된 제어 장치

- 연산과 명령어 수행 회로가 직접 구성된 제어 회로에 의해 기동하는 장치

- 마이크로 프로그램에 의한 제어 장치

- 레지스터

- 범용 레지스터와 특수 레지스터로 구분

- 특수 레지스터의 종류

- 누산기(AC)

- 기억 장치 버퍼 레지스터(MBR)

- 기억 장치 주소 레지스터(MAR)

- 프로그램 카운터(PC)

- 명령어 레지스터(IR)

- 처리 장치

- 연산 장치(ALU) + 레지스터

- 수행 되는 모든 연산의 기능은 비트 패턴으로 이루어진 마이크로 연산으로 구현

- 각 마이크로 연산은 처리 장치 내의 각종 논리 회로와 연결되어 하드웨어를 직접적으로 통제할 수 있는 제어 단어로 일대일 매핑 되어 있음

- 제어 장치

- 기본 기능

- 처리 장치를 구동해서 특정 연산을 수행한 후 처리 장치 내의 레지스터 값을 갱신하고 연산 결과를 출력

- 현재 명령을 수행한 후 다음에 수행할 명령의 주소 정보를 생성

- 명령어 사이클

- 인출 – 해독 – 실행 – 저장

- 구성 요소

- PC

- IR

- 명령어 해독기

- 주소 결정 회로

- 제어 기억 장치

- 제어 기억 장치 주소 레지스터

- 제어 기억 장치 데이터 레지스터

- 기본 기능

- 명령어의 구현 방법

- 입 출력 장치 및 병렬 처리

- 입 출력 시스템의 기본 구성 요소

- 입 출력 장치

- 입 출력 장치 제어기

- 입 출력 장치 인터페이스

- 입 출력 버스

- 입 출력 제어 방식

- CPU에 의한 방식

- 입 출력 장치의 정보가 CPU를 통해 주 기억 장치에 쓰고 읽혀지는 방식

- 프로그램에 의한 방식과 인터럽트에 의한 방식으로 구분

- 입 출력 장치의 정보가 CPU를 통해 주 기억 장치에 쓰고 읽혀지는 방식

- DMA 방식

- 입 출력 장치가 주 기억 장치와 직접 연결되어 CPU는 두 장치 간의 초기 설정 및 허가에만 관여하고 직접적인 정보의 이동은 장치 간에 DMA 제어기가 처리하는 방식

- 채널 방식

- 채널이라는 입 출력 전용의 별도 프로세서를 사용하는 방식

- 정보 전송 통로 제공 및 CPU와 같은 연산 작업도 수행 가능

- 채널이라는 입 출력 전용의 별도 프로세서를 사용하는 방식

- CPU에 의한 방식

- 병렬 처리

- 파이프라인 처리기

- 프로그램 내에 내재하고 있는 시간적 병렬성을 활용

- 하나의 연산을 서로 다른 기능을 가진 여러 개의 단계로 분할하여 각 단계가 동시에 서로 다른 데이터를 취급하도록 하여 처리 속도의 향상을 도모

- 파이프라인 처리기

- 입 출력 시스템의 기본 구성 요소